HLS 101 - 모든 RTL 하드웨어 디자인 팀이 알아야 하는 것

2020-07-02 10:30~12:00

Mentor, a Siemens Business / 이준석 차장

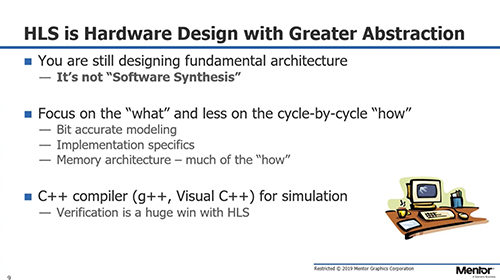

상위수준합성이란 C/C++/SystemC와 같은 추상화 수준이 높은 언어로 기술한 알고리즘 디자인을 RTL 하드웨어로 합성해 주는 것을 말합니다.

최근 컴퓨터 비전, 인공지능 머신러닝, 5G 통신 같은 응용분야에서는 상당히 복잡한 알고리즘이 필요합니다.

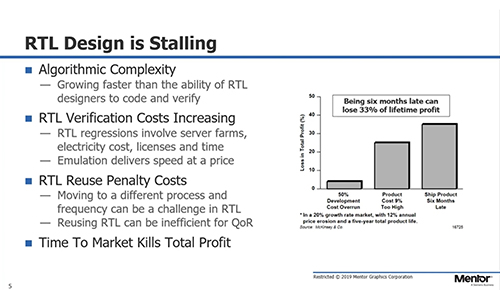

이처럼 복잡한 연산을 필요로 하는 알고리즘을 실제 하드웨어로 구현할 때 기존의 수작업 하드웨어 코딩방식으로 개발을 하게 될 경우 개발 기간이 상당히 길어지게 됩니다. 이는 제품 출시 시기의 지연이 발생하게 되고 개발팀이 얻는 이익은 줄어들 것입니다. 또한 최근 각광을 받고 있는 딥러닝을 이용한 영상처리의 경우 많은 산술연산과 메모리 엑세스를 요구합니다. 수만 수십만의 연산과 메모리 엑세스를 하드웨어로 아키텍처링하고 이를 수작업 코딩하여 하드웨어로 디자인 하는 것은 매우 어려운 일일 것입니다.

|

캐타펄트 HLS 솔루션은 C++/SystemC와 같은 상위수준언어를 입력으로 RTL을 구현합니다. 합성 가능한 디자인을 입력하고 설계자는 동작 주파수, 클럭, 리셋, 사용할 메모리의 종류와 같은 하드웨어 제약사항을 툴에 적용합니다.

Latency와 throughput 설계 사양을 만족하기 위하여 파이프라이닝, 루프 언롤링과 같은 아키텍처링을 툴의 옵션으로 진행합니다. 이처럼 캐터펄트는 설계자의 제약조건에 따라 최적화된 하드웨어 RTL을 구현할 수 있게 합니다. 또한 HLS는 기존 설계 플로우를 확장하고 하드웨어 설계에 대한 새롭고 강력한 접근 방식을 제공합니다.

사실 캐타펄트 HLS는 현재 SoC IP를 개발하는 RTL 엔지니어에게 가장 유용합니다. 보통C++/SystemC와 같은 상위수준의 언어로 RTL하드웨어를 만들게 되면 미래의 RTL 엔지니어는 내 일자리를 잃을 것이라고 크게 오해하는 경우가 많습니다.

그러나 현실은 전혀 그렇지 않습니다. 설계를 하는 언어의 추상화 수준이 높을 뿐 오랜 RTL 개발 경력으로 쌓은 하드웨어 적인 구조 분석과 이해는 HLS를 활용하였을 때 그 최적화의 수준이 월등히 높습니다.

|

만약 어떤 연산블록 내에서 여러 중첩된 루프내에서 메모리를 읽기와 쓰기를 반복적 필요로 하고 복잡한 연산으로 이어지는 설계가 있다고 가정해 봅시다. 이때 하드웨어적인 메모리 아키텍처를 고려한 HLS 설계가 된다면 적은 메모리로 설계 사양을 만족할 것이고요. 그렇지 않다면 불필요한 메모리를 더 많이 사용하게 되어 전체적으로 칩 크기에 대한 비용이 늘어나게 될 것입니다. 또한 상위수준의 언어로 기술함에 따라 설계 기간이 단축되고 그 만큼 검증에 투자하는 시간을 늘려 보다 완성도 있는 하드웨어 설계를 만들어 낼 수 있을 것입니다.

HLS분야에서 선두를 달리고 있는 저희 Mentor 지멘스 비즈니스의 Catapult 솔루션과 함께하는 웨비나에 참석하시어 유익한 시간 되시기를 바라겠습니다.

Sr. AE, HLS

이준석 차장

웨비나 댓글

- 46 Comments

- 김*균 (2020-07-03 오전 10:14:40)

- 감사합니다.

- 박*원 (2020-07-02 오후 5:11:47)

- 좋은 세미나 기대합니다

- 김*식 (2020-07-02 오후 12:36:06)

- 좋은 세미나 감사합니다

- 박*영 (2020-07-02 오전 11:18:15)

- 마침 시간이 나서 재방송 보고 있습니다. 고맙습니다

- 신*희 (2020-07-02 오전 11:00:21)

- 유익한 시간이었습니다. 감사합니다.

- 박*혁 (2020-07-02 오전 10:24:01)

- 재미있고 유익한 세미나 부탁드려요!

- 김*구 (2020-07-02 오전 8:45:07)

- 열심히 듣도록 하겠습니다.^^

- 이*승 (2020-07-02 오전 8:15:59)

- 좋은 방송 기대합니다.

- 최*휴 (2020-07-02 오전 7:57:34)

- 완전 기대합니다.

- 이*훈 (2020-06-30 오후 1:16:35)

- 유익한 시간 될 것 같습니다.